Computex 2021 | Alder Lake should be worried: AMD teases 3D V-cache on Ryzen 9 5900X, 192 MB 2 TB/s L3 cache results in 15% fps gains; Possible Zen 3+ Warhol incoming

During AMD's Computex 2021 keynote earlier today, CEO Dr. Lisa Su made a stunning disclosure that may have major ramifications in the days to come for the computing industry. Dr. Su announced that AMD will be producing 3D-stacked chiplets later this year. These chiplets come with stacked caches called 3D V-cache (vertical cache) that is expected to significantly boost gaming performance.

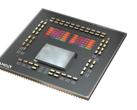

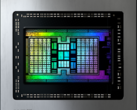

AMD's 3D V-cache allows stacking an additional 64 MB of SRAM cache vertically on top of each core complex die (CCD). For the current Ryzen 5000 series chips such as the Ryzen 9 5900X and the Ryzen 9 5950X, this means three such stacked 3D V-caches totaling a whopping 192 MB of L3 cache per processor.

AMD first revealed that it was exploring 3D stacking with X3D back during its 2020 Financial Analyst Day. This is actually a hybrid of 2.5D and 3D packaging called 3DFabric, which TSMC announced in during its 26th Technology Symposium in late 2020.

Today, Dr. Su showed a prototype Ryzen 9 5900X that features 3D cache stacking technology, and the first 1080p game benchmarks already seem to show around a 15% performance benefit on the current 7 nm Zen 3 architecture — something that is normally a characteristic of gen-on-gen upgrades.

The 3D V-cache is bonded to the CCD with through silicon vias (TSVs) that allow for power and data transer rates up to 2 TB/s bandwidth between the cache and the CPU. The prototype Ryzen 9 5900X that was shown had one of its CCD's exposed to show how the 3D V-cache would like. The 64 MB SRAM cache on the left CCD that was shown measures 6 mm x 6 mm.

The hybrid bonding with the TSVs allow for a >200x interconnect density than conventional 2D packaging, >3x interconnect efficiency compared to microbump 3D, and a >15% increase in density compared to microbump 3D. TSMC's 3DFabric technology uses direct copper-to-copper bonding to improve thermals, density, and pitch. Dr. Su said that this 3D interconnect is the most efficient and advanced active-on-active silicon technology of its kind.

A short demo of Gears 5 running on a conventional Ryzen 9 5900X (64 MB L3 cache) and the 3D-stacked Ryzen 9 5900X (192 MB L3 cache) with both CPUs locked at 4 GHz showed a 12% higher fps in the latter. Overall, the new 3D V-cache results in an average of 15% fps boost across several titles including DOTA 2 (Vulkan), Gears 5 (DX 12), Monster Hunter World (DX 11), League of Legends (DX 11), and Fortnite (DX 12) at 1080p (at 4 GHz).

In conclusion, Dr. Lisa Su said that AMD is ready to make the "highest-end" products using this 3D V-cache stacking by the end of this year. This demo is no doubt just a sample of what's to come. It remains to be seen whether AMD is planning to introduce initial SKUs featuring this tech as a "test lineup" of sorts before scaling up production for upcoming architectures. There is a high possibility that we may see this tech debut with Zen 3+ Warhol, which currently is rumored to be non-existent or canceled.

More importantly, if AMD is indeed planning to introduce such designs later this year, it may pose a serious threat to Intel's upcoming Alder Lake hybrid architecture, at least when it comes to gaming. Being able to reuse existing architectures is no doubt an area that will be keenly explored by chip makers. Will this technology be somehow leveraged with GPUs as well? We can't wait to know what's in store in the coming months.

Check out AMD's Computex 2021 keynote below from the 33:11 mark for Dr. Lisa Su's talk on 3D V-cache.

Source(s)

AMD Computex 2021 Event