Even though TSMC currently has its hands full with 7 nm EUV orders from all major high-tech companies around the world, the Taiwanese semiconductor manufacturer still has time for other endeavors. Its latest project was showcased at the VLSI tech symposium in Kyoto, and it looks like TSMC could soon impact CPU designs. However, the company is not interested in the mainstream markets, as the chip it revealed in Kyoto is targeted at high-performance computing applications.

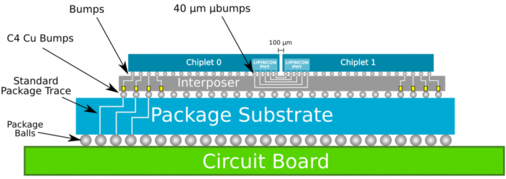

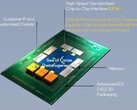

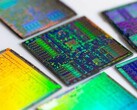

Leveraging the power of its own 7 nm nodes in conjunction with multiple custom-made high-speed cores designed by ARM, TSMC’s HPC chiplet design takes advantage of a few new proprietary technologies that include LIPINCON inter-chiplet connectors and CoWoS packaging. TSMC’s chiplet thus combines a cluster of smaller chipsets that are interconnected via high-speed meshes. This should allow for reduced production costs, provided the packaging techniques are efficient enough in this regard.

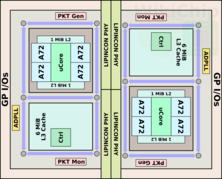

The proof-of-concept system presented by TSMC included two chiplets, each with four Cortex-A72 cores connected through a “bi-directional interconnect mesh bus” that operate at 4 GHz. The chiplets also have 2 MB L2 and 6 MB L3 memory caches. The interconnect itself integrates a Chip-on-Wafer-on-Substrate interposer that makes use of the LIPINCON (Low-voltage-In-Package-INterCONnect) architecture, which, in turn, operates at 0.3 V and has a bandwidth of 8 Gb/s per pin for a total of 320 GB/s. TSMC claims the bandwidth density for this design can reach 1.6 Tb/s/square-mm.

With the introduction of the LIPINCON architecture, TSMC hopes to provide a viable alternative for Intel’s AIB and AMD’s Infinity Fabric. Furthermore, the Taiwanese company believes that the first commercial processors to integrate the LIPINCON architecture could arrive next year.

I first stepped into the wondrous IT&C world when I was around seven years old. I was instantly fascinated by computerized graphics, whether they were from games or 3D applications like 3D Max. I'm also an avid reader of science fiction, an astrophysics aficionado, and a crypto geek. I started writing PC-related articles for Softpedia and a few blogs back in 2006. I joined the Notebookcheck team in the summer of 2017 and am currently a senior tech writer mostly covering processor, GPU, and laptop news.

> Expert Reviews and News on Laptops, Smartphones and Tech Innovations > News > News Archive > Newsarchive 2019 10 > TSMC and ARM reveal 7 nm high-performance computing interposer chiplet

Bogdan Solca, 2019-10- 1 (Update: 2026-02-18)