Courtesy of numerous leaks and rumors, there is little we don’t know about the Strix Point and Strix Halo APUs. For instance, we recently reported the performance of the top-of-the-line Strix Point SKU. However, aside from revealing that the Strix APUs will rely on a Zen 5 CPU and an RDNA 3+ iGPU, AMD has yet to officially confirm details such as Compute Unit count, cache sizes, etc.

Today, we have what seem to be official Strix Point and Strix Halo specifications thanks to a leaked AMD document posted online and subsequently spotted by HKEPC.

AMD Strix Halo: 16 full Zen 5 cores + RDNA 3.5

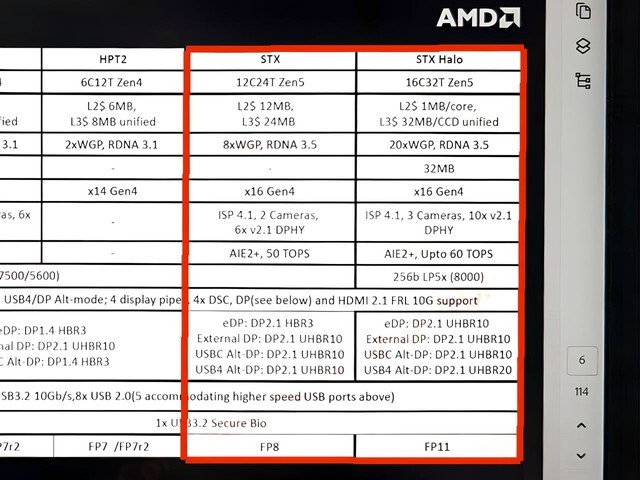

Kicking things off with Strix Halo, AMD’s next-gen flagship APU is apparently chiplet-based and tops out at 16 Zen 5 cores distributed among two CCDs and 32 threads. Each CCD will have 1 MB of L2 per core and 32 MB of L3 cache. So, we are looking at 16 MB of L2 and 64 MB of total L3 cache.

On the GPU side, Strix Halo’s RDNA 3.5 iGPU reportedly carries 20 WGPs or 40 CUs. The RX 7600 XT, for example, only has 32 CUs. To that end, leaks have pointed to Strix Halo being faster than the RX 7600 XT (Available on Amazon).

Additionally, there appears to be 32 MB of MALL (Memory Attached Last Level) cache. The presence of 32 MB of MALL cache should bode well for Strix Halo APUs since iGPUs are often starved for memory bandwidth because of a lack of dedicated VRAM.

Other notable details include support for LPDDR5X-8000 RAM and an NPU with up to 60 TOPs of compute.

Finally, the Strix Halo APUs seemingly have a power budget of 70 W with AMD allowing the chips to be configured at up to a 130 W TDP.

AMD Strix Point: Hybrid design with Zen 5 + Zen 5c

Unlike Strix Halo, the mainstream Strix Point APUs are allegedly monolithic and employ a hybrid design with a mix of standard Zen 5 and smaller Zen 5c cores. The CPU apparently tops out at 12 cores/24 threads with each core carrying 1 MB of L2 cache. There will be 24 MB of total L3 cache.

On the graphics side, the RDNA 3+ iGPU reportedly features 8 WGP or 16 CUs without any MALL cache. So, while we can expect much better performance than the current Radeon 780M, the Strix Point chips will fall considerably short of the Strix Halo products owing to their cut-down nature and bandwidth limitations.

Finally, the Strix Point APU’s NPU supposedly only goes up to 50 TOPs and the chips will range from 45 W to 65 W.

AMD is expected to announce the Strix Pont APUs later this year, possibly at Computex in June. So, we won’t have to wait too long to find out what kind of performance the Strix chips bring to the market.

![AMD Strix Point Zen 5 mobile processors could launch in August (Image source: AMD [edited])](fileadmin/_processed_/8/d/csm_AMD-Strix-Point-Zen-5-mobile-processors_9e48158631.jpg)