AMD will be launching the 7nm++ Zen 3-based Ryzen 4000 CPUs for desktop later this year. While Zen 3 belongs to the optimization phase of AMD's inflection-optimization cycle, it is still expected to bring some core architecture improvements. We have been hearing about the purported IPC gains in Zen 3 for quite some time now, and the latest report from AdoredTV further confirms them.

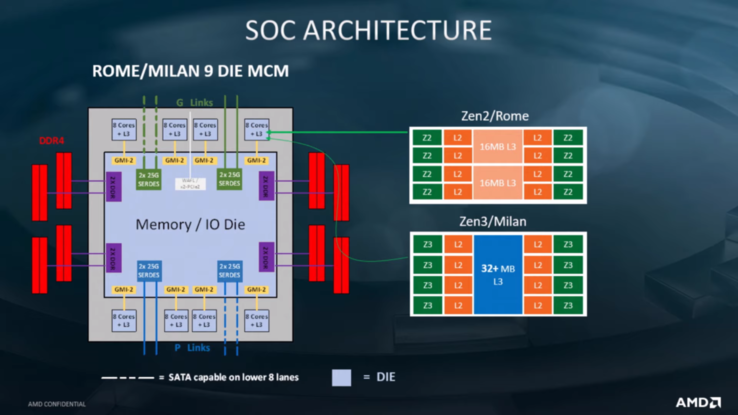

According to AdoredTV's sources, the IPC gains in Zen 3 will be on par with that of Zen 2, which is between 10-15% per thread. Multi-threaded workloads could still see larger IPC gains. Zen 3 will also introduce a new CCX design, which could be among those core architecture improvements Dr. Lisa Su had alluded to earlier. Zen 3 will have one CCX with eight cores with a single L3 cache at 32 MB per CCX. Larger caches such as 48 MB or 64 MB are not indicated. With the new cache design, more number of cores now have access to a common L3 cache on the same die. This will likely reduce latency and improve gaming performance. Zen 3 will continue to use SMT-2 and not SMT-4 as was rumored earlier.

Previous reports indicated that Zen 3 could offer up to 8% IPC improvements and some reports even said that the number could be, in fact, higher than 15%. However, is now becoming increasingly clear that the IPC improvements per thread would be in the 10-15% range, which is nothing to scoff at.

Also being confirmed is something that we had reported back in December 2019 — that the 5nm Zen 4 Ryzen 5000 will herald the beginning of a new socket. New information we have now is that Zen 4 will feature more cores, a 1 MB L2 cache, AVX 512 support, and will look to offer much improved IPC.