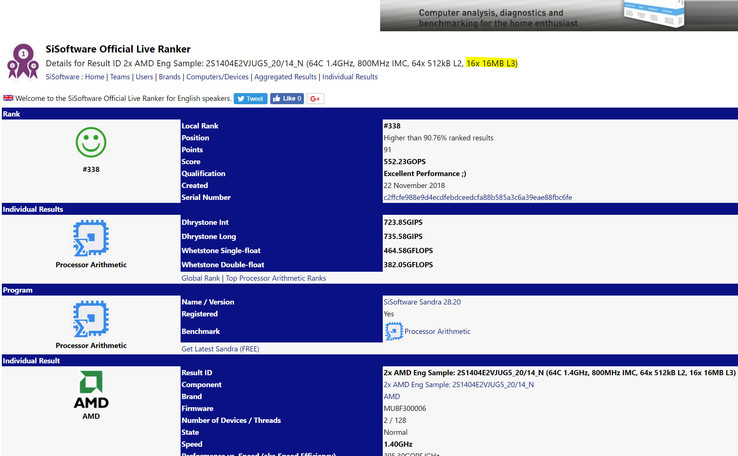

From what we’ve heard about AMD’s upcoming “Rome” EPYC CPUs, Team Red has quite the beast on their hands. AMD has confirmed that Rome will be an 8-die, 64-core monster. A recent Cinebench score leak of a dual-socket Rome system showed off the CPU’s processing prowess. Now, an alleged SiSoftware SANDRA database entry states that Rome will have double the L3 cache per CCX as Zen chips, bringing the total to a whopping 256 MB per chip.

The Zen architecture organizes L3 cache into chunks that are shared between CCX units (blocks of four cores). Zen was designed such that each CCX unit had 8 MB of L3 cache shared between its four cores. According to the SiSoftware SANDRA entry, Rome (which is based on the new Zen 2 architecture) doubles this amount of shared L3 cache to 16 MB per CCX. SANDRA detected the L3 cache structure of the tested Rome system as “16 x 16 MB L3,” as opposed to the usual “N x 8 MB L3” seen with Zen CPUs. (For example, the 8-core, 2 CCX Ryzen 7 2700X lists its L3 cache as “2 x 8 MB L3.”)

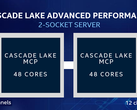

If this reading is accurate, it would peg the total L3 cache available on each Rome chip at a massive 256 MB across its 64 cores. Couple this with Rome’s 7 nm process and Rome will be a major competitor in the server CPU space. Considering that Intel’s current plans for their upcoming Cascade Lake-SP CPUs (which will compete directly with AMD’s Rome chips) cap the core count at 28 and the total L3 cache at 38.5 MB, AMD may easily overpower their rival this generation.

That all being said, this is still a rumor and should not be taken as gospel until we hear otherwise from AMD. It’s possible that SANDRA read the system information incorrectly, but considering that Zen 2 is more of a redesign than an improvement, it’s not out of the realm of possibility to see a change in L3 cache management.

Source(s)

SiSoftware SANDRA Database (link now inactive, see picture above)