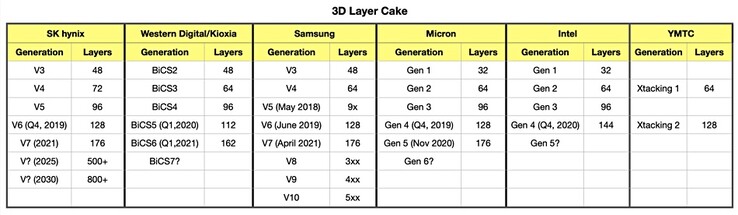

Western Digital and Kioxia announced this week that they have completed development for the Gen 6 BiCS (Bit Cost Scaling) 3D NAND storage memory chips for SSDs. Gen 6 ups the layer count from 112 to 162 and also allows for 40% smaller dies with reduced cost per bit and up to 70% more manufactured bits per wafer over Gen 5.

The smaller memory dies are now possible thanks to innovations in vertical as well as lateral scaling. In this respect, Gen 6 improves the lateral cell array density by 10%. The new generation also integrates Circuit Under Array CMOS and four-plane operation, which considerably improve write speeds by 2.4X and lower read latency by 10% compared to Gen 5 specs. I/O performance is also boosted by 66%, from 1,066 MT/S to 1600 MT/s. These speeds match what SK Hynix, Micron and Samsung already achieved with their 176-layer 3D NAND generations. YMTC still lags behind with 128 layers, while Intel sold the 144-layer technology and any subsequent prototypes to SK Hynix last year.

We can expect to see the first SSDs with the 162-layer 3D NAND chips some time in Q1 2022. By then, WD and Kioxia could already announce Gen 7 with 250+ layers, and, if the roadmaps provided by SK Hynix are to be respected, we should be seeing 500+ layers by 2025 and more than 800 layers within the next 10 years.