SuperFin transistors — The +'s now have fancy names

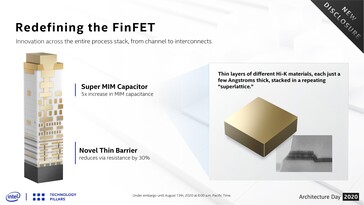

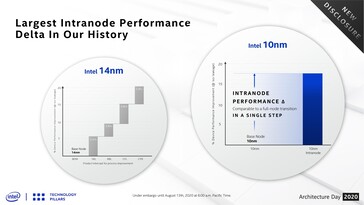

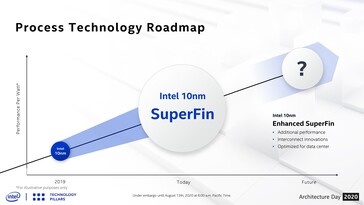

One of the main enhancements that Intel stressed upon during the Architecture Day press brief was the new SuperFin transistor. While previous 14 nm FinFET processes allowed for a maximum of 5.9% intra-node performance delta, Intel said that the transition to 10 nm SuperFin allowed for greater than 15% intra-node delta from the base node, which is comparable to a full node transition. SuperFin uses a new capacitor design called SuperMIM (metal-insulator-metal), which delivers 5x the increase in MIM capacitance.

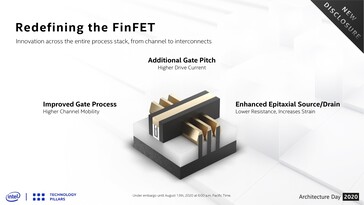

SuperFin will offer an improved gate process (for higher channel mobility), additional gate pitch (to drive higher current), and an enhanced epitaxial source/drain (to lower resistance and increase strain). Intel finally did acknowledge that the current naming convention in process improvements does have potential for confusion. Consumers may not know how a 14 nm++ node differs from the base 14 nm or 14 nm+ one. Going forward, Intel will be using defined nomenclature for intra-nodal improvements. For instance, the upcoming refinement to the 10nm SuperFin node will be called 10nm Enhanced SuperFin. Intel is currently optimizing this node for data center use.

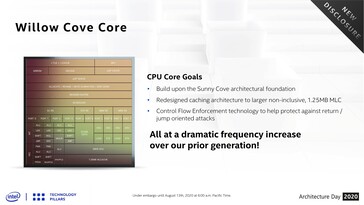

Willow Cove cores — Better VF curves compared to Sunny Cove

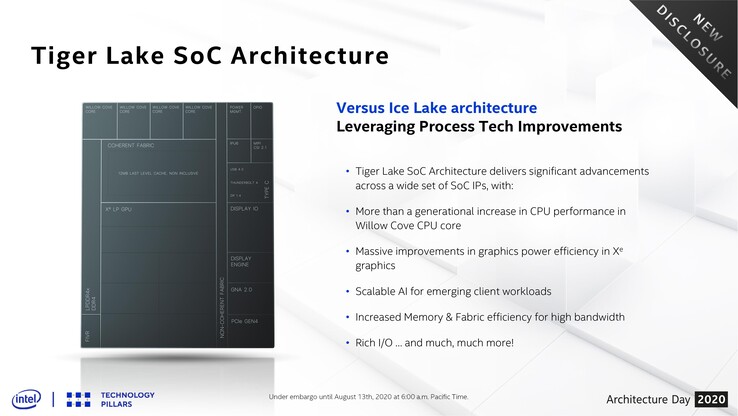

We have managed to garner quite a bit of information pertaining to Tiger Lake and the Xe LP GPU in several leaks so far. Still, it is always good to hear straight from the horse's mouth. Willow Cove builds upon the 10 nm Sunny Cove architecture but comes with a redesigned middle-level cache (MLC) of 1.25 MB.

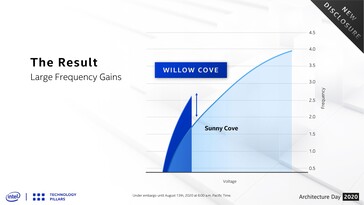

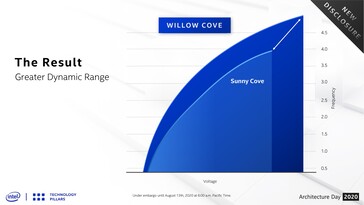

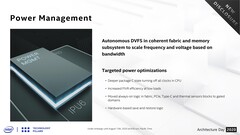

The biggest benefit with Willow Cove is that it can now deliver higher frequencies at relatively lower voltages. This directly results in improved power efficiency and an overall greater dynamic range compared to Sunny Cove

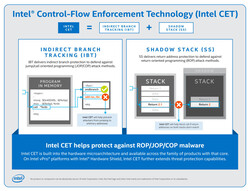

Also being implemented is a control-flow enforcement technology (CET) that prevents against return/jump oriented attacks. Intel detailed about CET back in June this year and confirmed that the protection was coming for the first time to Tiger Lake CPUs. Intel has been working on CET since at least 2016, so it should not be construed as a measure against Spectre and Meltdown attacks. However, it is possible that CET confers an additional layer of security to prevent such attacks. CET is supported in the Windows 10 2004 update.

Other platform features

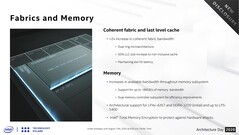

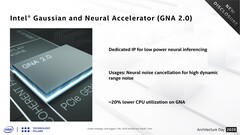

Willow Cove now offers a 2x increase in coherent fabric bandwidth. Memory support is available for LPDDR4x-4267, DDR4-3200, and LPDDR5-5400 RAM along with a maximum of up to 86 GB/s memory bandwidth. Willow Cove will also offer an improved Gaussian and Neural Accelerator (GNA) 2.0 that is a dedicated IP for low power neural inferencing with up to 20% lesser CPU utilization.

Previously, we had detailed about some of the display enhancements coming to Tiger Lake including hardware accelerated 12-bit VP9/HEVC encode/decode along with a new fully integrated voltage regulator (FIVR) power delivery architecture. Intel confirmed that Tiger Lake's IPU6 unit can drive video up to 4K90 resolutions and process still images up to 42 MP. Thunderbolt 4 and USB4 support come integrated on die. Tiger Lake also features PCIe Gen4 support with up to a 100 ns lower latency when a PCIe device is connected to the CPU instead of the PCH.

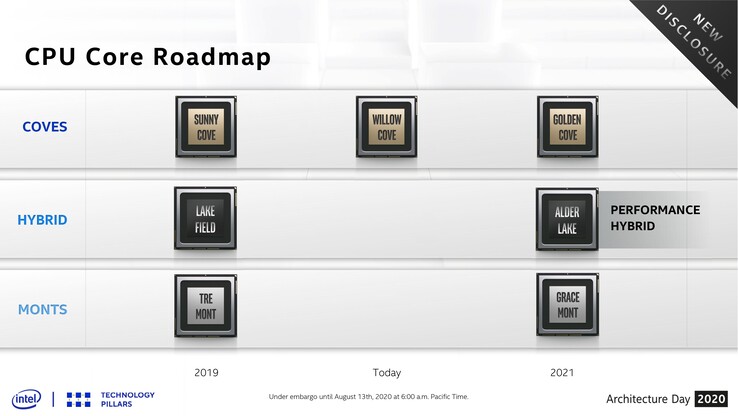

Introducing Alder Lake — A performance hybrid CPU

Intel recently introduced a power-efficient hybrid platform with Lakefield. Next year, Intel will be introducing a performance variant called Alder Lake. Intel did not delve into specifics of Alder Lake, but we already know that Alder Lake will be bringing a big.LITTLE-esque architecture comprised of performance Golden Cove and power-efficient Gracemont cores on an LGA 1700 socket. Core configurations up to 8+8+1 (8 big cores, 8 small cores, and one GT1 graphics) and up to 12 such combinations are expected. Alder Lake will also see the debut of scheduling improvements on the OS side of things. A hardware-guided OS scheduler to better target specific cores for specific instruction sets is expected, but Intel didn't delve into details.

Source(s)

Intel Press Brief