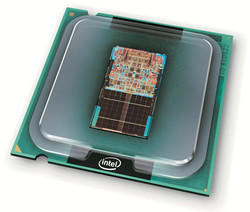

Core 2 Duo notebook processor (CPU)

The Intel Core 2 Duo (also known as Core2 Duo) notebook processor is a 64 bit dual core processor. This means two processor cores work inside a Core 2 Duo in parallel.

The Core 2 Duo, which was introduced on July 27 2006, is the direct successor of the Core Duo. Each core is based on the Pentium M micro architecture. Compared with the old Netburst architecture of the Pentium 4, the cores in the Core 2 Duo have shorter pipelines. As a result, the maximum clock rate is lower but the performance per clock is significantly higher. Thus a Pentium 4M with the same clock rate is up to 40% slower.

Both, the notebook Core 2 Duo and the desktop Core 2 Duo are based on the same processor. However, the notebook version runs with a lower voltage (0.95 to 1.188 volt) and a lower front side bus (1066 vs. 667 MHz). As a result (and because of slower laptop hard discs) the performance of notebooks is about 20% lower than their desktop counterparts with the same clock rate.

Key Features

- 64 bit support

- Dual core processor with shared level 2 cache

- Execute Disable Bit

- Partially Intel Virtualization Technology (VT)

- Socket M (starting from Santa Rosa socket P)

- 291 million transistors

Performance

The performance of the Core 2 Duo processor in comparison with its direct competitor, the AMD Turion 64 X2, is very good. The Core 2 Duo beats the AMD Turion 64 X2 with the same clock rate in virtually all applications (on average by 15%). The energy consumption is similar in both processors. In comparison with the predecessor Core Duo, the Core 2 Duo is about 10% faster and consumes a bit more energy (More details further below).

Specifications

The Core 2 Duo processors are produced in 65 nm (and later in 45nm), contain 14 stages pipelines and 2-4 MB level 2 cache (depending on the model). The features of the Core 2 Duo are:

x86 architecture

The Intel Core 2 Duo uses the x86 instruction set, which was introduced in 1978 with the 8086/8088 processor. Furthermore it supports the multimedia extension MMX, SSE2, SSE3 and SSE4.

Dual core technology

Two processor cores run with the same frequency in the same processor building block and share the level 2 cache as well as the front side bus (FSB).

Execute Disable Bit

Prevents security problems through buffer overflows, if the operation system supports it and if it is activated.

Wide Dynamic Execution *

Every core can execute four complete commands simultaneously.

Smart-Memory-Access *

Shorter idle times, improved data transfer and faster out-of-order command execution lead to better usage of the pipeline and as a result to higher performance.

Advanced-Smart-Cache *

Like the Core Duo, the Core 2 Duo has shared level 2 cache and each core receives the same amount of cache. Intel doubled the bandwidth to the level 1 cache though.

Advanced-Digital-Media-Boost *

One 128-Bit SSE command is now output per clock cycle.

Virtualisation technology (VT)

The Intel VT offers hardware support for virtual systems on one computer (use of several isolated operation systems at the same time e.g. through Xen or VMWare).

Beware, not all models support VT (especially the cheaper ones dont).

64 bit support *

Support of 64 bit wide words in the CPU. This means the processor can handle 64 bit data packets. The Intel Core 2 Duo supports the AMD64 extension (licensed), through which 32 and 64 bit programs can run on the CPU (if a 64 bit operation system is used).

Theoretically, a 64 bit processor can access more than 4 GB of memory, but this is usually limited by the chip set used.

* This feature was newly introduced with the Core 2 Duo.

Energy saving functions

Like with the previous version, the clock rate and voltage can be set dynamically and individually for each core (Speedstep). Under light load the processor can save energy by lowering the clock speed (to 1200 MHz respectively 800 MHz with the Santa Rosa) and the core voltage (from 1.3 Volt to 1.0375 Volt). This happens with virtually no performance losses, thanks to the automatic adjustment of the clock speed. Additionally, the processor can turn off parts of the CPU which are not used, to save energy.

Intel Dynamic Power Coordination

Coordinates the Enhanced Intel SpeedStep technology and the Idle Power-Management State (C-state) transitions independent of the core.

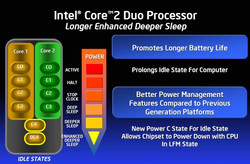

Enhanced Intel Deeper Sleep with Dynamic Cache Sizing

Writes data from the cache to the main memory during inactivity. As a result, the CPU voltage can be lowered which saves energy.

Intel Dynamic Bus Parking

Allows the chip set to shut down during inactivity to save energy.

Advanced Power Gating

Parts of the CPU core can be shut down through "Advanced Power Gating". This can even happen if performance is required, to improve the performance per watt ratio.

Enhanced Deep C4 Sleep State

The core voltage can be further reduced, if the level 2 cache is turned off.

Split Bus Array

Buses and arrays are separated in order to set them individually into energy saving mode during certain operation states.

Santa Rosa update

On Mai 9th 2007 the Core 2 Duo processor was upgraded for the 4th Centrino generation called Santa Rosa. The processor is still based on the Merom core, but some energy saving functions and optimisations were added. Furthermore, it now needs the socket P with 478 pins, which isn't compatible with the socket M of the older Core 2 Duo.

In contrast with its predecessor, the new Core 2 Duo processors now run with a 800 MHz FSB (200 MHz quad-pumped) instead of 667 MHz (133 MHz quad-pumped).

The FSB now supports "Dynamic front side bus switching", whereas the FSB can be lowered from 200 MHz to 100 MHz under light processor load, to save energy. This drop only affects the chipset and CPU and is thus called "virtual". With speedstep, the Core 2 Duo can slow down to a minimum of 1.2 GHz. Thanks to the lower (virtual) FSB, the "Santa Rosa" Core 2 Duo can drop even more, to 800 MHz, to save even more energy.

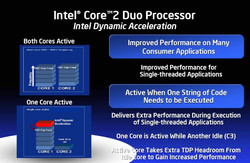

Another new feature is the dynamically overclocking of the core, called "Dynamic Acceleration". If only one core is used, it can be dynamically overclocked, while the second core stays in the energy saving C3-modus. Therefore the overclocked core can work with the clock speed of the next higher model (e.g. 2.2 instead of 2.0 GHz with the T7300), without any change in the TDP (thermal design power) and without the need for more cooling.

If idle, the processor will start one of the various saving modes (C1 to C4/DC4). The chipset of the Santa Rosa keeps the processor as long as possible in energy saving mode (e.g. by preventing memory acces).

Penryn Update

In Jannuary 2008 Intel introduced the new T9xxx and T8xxx Core 2 Duo processors of the new "Penryn" core. These CPUs are produced in 45nm (instead of the 65nm before) and offer a bigger Level 2 Cache (3 and 6 MB versus 2 and 4 before). Furthermore, the Penryn core has a faster division engine and 47 new SSE instructions (SSE4). Due to the 45 nm process, Intel was able to increase the core speed without increasing the current consumption.

Compared to a similar clocked Merom Core 2 Duo, the Penryn is on average between 5-10% faster. The speed increase is mostly because of the bigger L2 Cache. Detailled benchmarks of the new Penryn CPUs can be found in our Intel Core 2 Duo Penryn review.

Downward compatibility

The Core 2 Duo prior to the introduction of Santa Rosa is, like its predecessor, still based on the PGA socket-M interface. It is thus possible, to upgrade some notebooks from Core Duo to Core 2 Duo. However, a Bios which supports the Core 2 Duo is necessary and the processor must not be soldered to the Mainboard (which is the case with the BGA - ball grid array - case).

Following chipsets theoretically support a Core 2 Duo:

Intel 945GM: Core 2 Duo, LV, ULV

Intel 945GMS: Core 2 Duo LV und ULV

Intel 945PM: Core 2 Duo, LV, ULV

Intel 940GML: Doesen't support the Core 2 Duo

Core Duo versus Core 2 Duo

The Core 2 Duo (Merom) architecture shows several advantages compared with the Core Duo (Yonah). Especially the 64 bit extension allows now the use of 64 bit operation systems and thus 4 GB memory (limited by the chipset). Furthermore, the Merom got a bigger level 2 cache and the architecture was widened:

- An additional "Simple Decoder"

- Maximum Decode Rate 4+1 compared with 3 of the Yonah core

- 96 to 80 entries in the reorder buffer

- +1 issue ports (6 versus 5)

- 32 scheduler entries (versus 24)

- Seperated FP Units

- 3 SSE Units (Yonah 1)

- An additional integer ALU

Furthermore, the pipeline was extended from 12 to 14. This allows a higher clock rate but means the speed per clock is lower (this is compensated by the afore mentioned widening of the architecture). [Source]

The benchmarks in our performance comparison between Core Duo T2400 and Core 2 Duo T5600 showed results ranging from -0.3% to 34% (on average about 10%). The energy consumption rose significantly however, which might be caused by the early Bios. > read the report

Models

The energy consumption of the processors is shown in the letter in front of the type number:

X ... Extreme (fastest) version with the highest energy consumption, see next paragraph

E ... >=55 watt (desktop)

T ... 30-39 watt (standard version in notebooks)

P ... max 25 watt

L ... 12-19 watt (low voltage)

U ... <11.9 watt (ultra low voltage)

The following 4-digit number shows built (first number) and performance (the other three numbers). The Core 2 mobile processors are supposed to get 5XXX and 7XXX (currently T2XXX for Core Duo and T1XXX for Core Solo).

The Core 2 Duo was introduced on July 31st 2006 (the FSB 800 version with DAT - Dynamic Acceleration Technology on May 9th 2007). Apart from that, starting from the middle of 2007 the topversion is called Core 2 Extreme X.

A detailed list of all current models is here: Mobile processor overview.

A list of all mobile processors according to performance is here: Benchmarklist of mobile prozessors.