We have not even seen any PCIe 5.0 implementations yet, and PCI SIG appears to be well on its way to finalizing the PCIe 6.0 specs. It looks like Gen 6 could indeed be ready some time in 2021, which means that Gen 5 will be a short-lived standard, just like PCIe 4.0. Of course, actual consumer implementations may only arrive by 2023 at the earliest, since the PCIe 5.0 standard is expected to see AMD / Intel adoption in about a year from now.

PCI SIG recently released version 0.7 for the PCIe 6.0 specs. This version basically includes the complete specs, so no new features can be added from this point onward. Additionally, the electrical specs are now set in stone as they are currently validated via test chips.

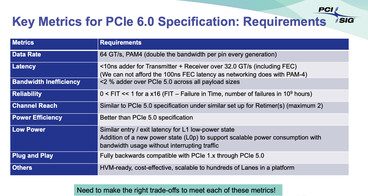

Some of the highlights for the PCIe 6.0 features include:

- 64 GT/s per pin for a maximum bandwidth of 256 GB/s on 16 lanes (essentially doubling that of the PCIe 5.0 standard and quadrupling the current PCIe 4.0 speeds)

- PAM4 (Pulse amplitude modulation on four levels) is now used for signaling. This tech is also used in high-end networking equipment with the InfiniBand communications standard or the GDDR6x VRAM modules integrated in Nvidia’s high-end GPUs

- Low-latency forward error correction (FEC) which is supposed to be lower than 10 ns

- Increased reliability over the Gen 5 standard

- Optimized power efficiency

- Scalable to hundreds of lanes on a single platform

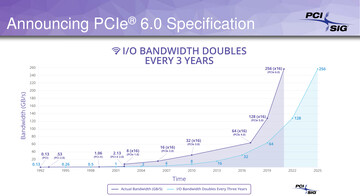

Interestingly enough, PCI SIG also released a graph showing plans to double the bandwidth every 3 years. These were the original plans delineated back in 2016. Apparently, this initial roadmap has changed in the meantime, as we now see a bandwidth doubling planned for every 2 years in a bid to increase transfer rates at an increased pace. Unfortunately, consumers will not be able to benefit from every generational leap right away, since AMD and Intel do not seem to be willing to adopt the standards that fast.