The RAM standards are now transitioning to the DDR5 era that brings quite a few improvements and considerable performance boost compared to DDR4. However, DDR and its faster GDDR relative are not really that fast compared to the HBM (high-bandwidth memory) standard, which, according to SK Hynix CEO Seok-Hee Lee, could be the foundation for the natural merger between CPUs and RAM.

At the Institute of Electrical and Electronics Engineers’ International Reliability Physics Symposium, Seok-Hee Lee presented his vision for a faster memory standard that would require a “convergence of memory and logic.” Lee presents a more gradual evolution starting with HBM:

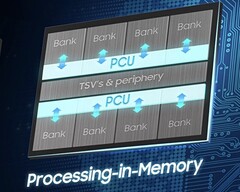

As the speed was increased in high-bandwidth memory by increasing the number of channels between the CPU and the memory, the speed will increase further in Processing Near Memory (PNM), where both the CPU and the memory exist within a single module. The speed will further increase in Processing In Memory (PIM), where the CPU and the memory exists within a single package. Ultimately, speed will increase further in Computing in Memory(CIM), where the CPU and the memory is integrated within a single die, to deliver high performance computing system.

SK Hynix is currently the second largest memory maker in the world, but it does not make any other type of chips like CPUs. Thus, CEO Lee calls for a collaboration between semiconductor giants in order to form an ecosystem that can sustain the new CPU+RAM hybrids: “Only by establishing a strategic partnership for Open Innovation based on collaboration and sharing with customers, suppliers, academia and government, we can shape a new era, which pursues both economic and social value.”

Lee also presented a new standard called Compute Express Link (CXL) that could complement the PCIe bus. The CXL memory is capable of moving data quickly and more efficiently between CPU and graphics / compute accelerators or smart network interfaces. “CXL memory is being prepared as a solution that not only expands bandwidth and capacity but also realizes the value of a persistent memory, [...] a solution to narrow the gap between the memory performance and the industry requirements.”

Last but not least, Lee touched upon the efforts that are being made to improve the NAND memory chips integrated in SSD storage solutions. With the jump to 10 nm nodes and below, SK Hynix may eventually be able to produce 600-layer NAND chips, which should greatly increase storage capacity and data transfer speeds over the current 176-layer cap.

Buy the SAPPHIRE NITRO Radeon R9 Fury with 4 GB HBM on Newegg