Stanford University and MIT joined forces to develop the first 3-D chip that integrates RAM into a CPU chip built with carbon nanotubes. This technology can be used to overcome bottlenecks in communication between logic circuits and memory blocks.

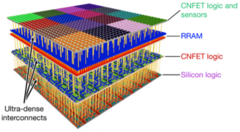

The 3-D chip is detailed in a paper published in the well-known journal Nature. MIT/Stanford claim that the 3-D chip fundamentally changes the way transistors are fabricated. Present day transistors are made of silicon, but the new ones proposed by MIT/Stanford are made of graphene nanotubes. These make up the logic layer (CNFET layer) inside the 3-D chip. The other layer consists of a new kind of memory called "resistive random-access memory" (RRAM), which works by altering the resistance of a solid dielectric material. According to H.-S. Phillip Wong, co-author of the research, "RRAM can be denser, faster, and more energy-efficient compared to DRAM."

The logic and memory layers are alternating, and in-between each of these layers there are "ultradense" wires that act as communication lanes. Even though the carbon nanotube chip designed by MIT/Stanford is very slow compared to current multi-core CPUs, project lead Max Shulaker claims that more complex designs are just a matter of time. Still, the 3-D chip integrates "over 1 million RRAM cells and 2 million carbon nanotube field-effect transistors, making the most complex nanoelectronic system ever made with emerging nanotechnologies.”

Loading Comments

I first stepped into the wondrous IT&C world when I was around seven years old. I was instantly fascinated by computerized graphics, whether they were from games or 3D applications like 3D Max. I'm also an avid reader of science fiction, an astrophysics aficionado, and a crypto geek. I started writing PC-related articles for Softpedia and a few blogs back in 2006. I joined the Notebookcheck team in the summer of 2017 and am currently a senior tech writer mostly covering processor, GPU, and laptop news.

> Expert Reviews and News on Laptops, Smartphones and Tech Innovations > News > News Archive > Newsarchive 2017 07 > MIT and Stanford present a 3-D chip that integrates CPU and RAM

Bogdan Solca, 2017-07-12 (Update: 2026-02-18)