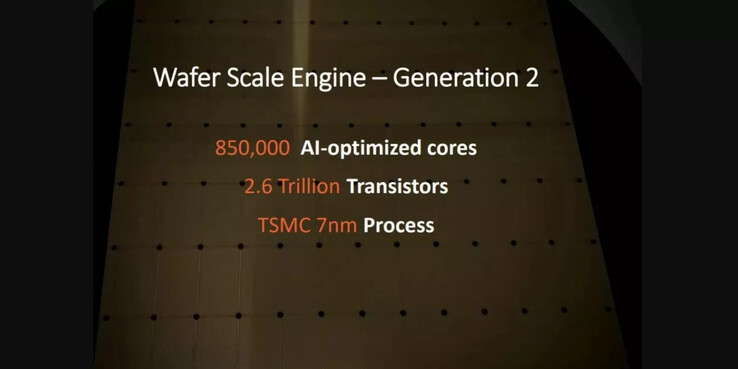

Cerebras breaks own record with improved densities via TSMC's 7 nm nodes: 2.6 trillion transistors and 850,000 cores on a single chip

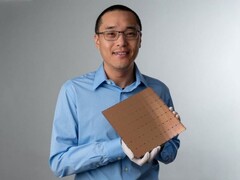

Remember the huge 8x9-inch chips integrating 1.2 trillion transistors and 400,000 cores announced by Cerebras Systems last year? Those are about to become obsolete, as the company has recently announced that it has updated the Wafer Scale Engine (WSE) technology to benefit from TSMC’s 7 nm production nodes instead of the older 16 nm FF nodes, which would lead to improved densities.

At this year’s Hot Chips event, Cerebras teased the updated WSE, revealing only that the improved chips can now integrate 2.6 trillion transistors and 850,000 cores. Since Cerebras is now using the improved 7 nm nodes from TSMC, we are assuming that the size of the chip will not increase too much from the current 46,225 square millimeters, if at all. This also depends on the amount of SRAM memory that will be added for each core cluster. The first gen WSE included 18 GB of on-chip SRAM with 9 PB/s bandwidth, so we are expecting that amount to be doubled with the new generation, at least in regards to the memory capacity.

When it comes to chip bandwidth, things are not that clear-cut anymore, since Cerebras did not mention anything regarding possible improvements to the communication fabric that stitches together all the smaller chips. First gen WSE was capable of 100 Pb/s total fabric bandwidth.

Power requirements will most likely be kept as close to the original 15 kW as possible, since the jump from 16 nm to 7 nm should reduce power requirements by around 100%.

More details on the improved Wafer Scale Engine should be unveiled in the coming months, and Cerebras reports that it is currently running the new monolithic chips in its labs.