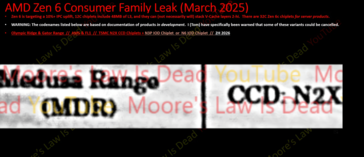

Leaker Moore's Law is Dead has followed up on his AMD Zen 6 leaks with some interesting new information about Medusa Ridge desktop parts. Previously, Tom stated Zen 6 would increase the number of cores per CCD to 12 and L3 cache to 48 MB. The new leak talks about its clock speeds, process node and hints at a 128-bit memory controller.

Olympic Ridge's (formerly known as Medusa Ridge) CCD will supposedly manufactured on TSMC's cutting-edge N2X node. N2X is said to be a high-performance variant of N2P. TSMC's roadmap doesn't specify how the two are different, but confirms it will start mass production in 2026, right around when AMD will unveil Zen 6 desktop SKUs. Its I/O die, on the other hand, could be made on TSMC N3P or N6.

Zen 6 essentially represents a two-node skip from TSMC N4 (Zen 5) to N2X. AMD has decided to go all-in on the bleeding edge after historically staying a node or two behind it. While this is great for performance and is rumoured to result in a 10% IPC uplift, N2 wafers aren't exactly cheap, and this extra cost will almost certainly trickle down to end users.

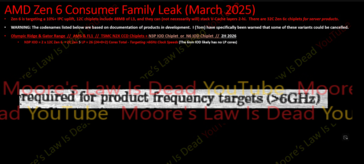

Tom says AMD management wants to push Zen 6 to the coveted 6.0 GHz mark, something Intel already achieved with Raptor Lake. Additionally, Zen 6 will have the ability to stack multiple 3D V-cache tiles on top of each other. Some server-grade parts might debut it, but the tech is unlikely to trickle down to gaming SKUs until Zen 7.