So far, we have seen Intel toy around with the hybrid CPU concept first with Lakefield and now with the upcoming Alder Lake. It looks like AMD could also be working on its own hybrid or heterogeneous processor, according to a recent patent discovered by @Underfox3.

The patent, filed in 2017 and titled "Instruction subset implementation for low power operation", can be accessed from the Free Patents Online site (Source link below). It details a CPU design that includes both high-power and low-power instruction set architectures (ISAs) on the same PCB. The patent offers three ways of achieving a hybrid CPU solution; each way differs in how the shared cache and registers are implemented.

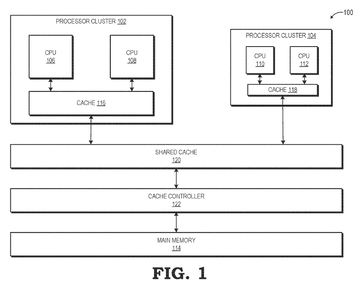

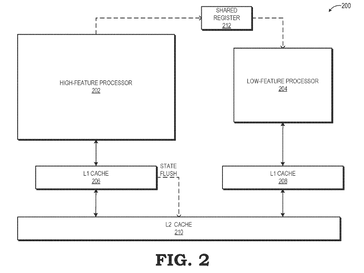

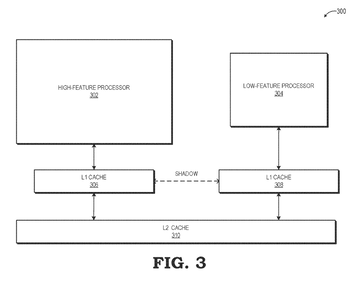

The patent drawings indicate "processor clusters" that have their own independent caches. In the first method, both these clusters interface with a shared cache, which then interacts with the cache controller and subsequently, the RAM. The second method looks at the possibility of using a shared register between both the CPU clusters. The clusters have their own independent L1 caches but can interface with a common L2 cache. The final alternative is similar to the second method but looks at shadow writing the thread state to the cache of the second CPU cluster. This enables the high-power cluster to immediately start executing the thread from the stored shhadow thread state as soon as it receives the go-ahead from the low-power cluster.

The patent seems to suggest that this design is intended for mobile devices, so it may not make it to desktops (if it indeed materializes, that is). This is unlike Intel, which is already developing up to 12 different core configurations for Alder Lake-S that is scheduled to drop some time next year. @Underfox3 notes that the patent is still in the adjustment process, so things can get tweaked down the line.

It is not yet clear when this patent would materialize as a commercial product. It is also too early to speculate on what kind of cores would the high and low performance clusters would feature. Back in May, @KOMACHI_ENSAKA leaked an AMD roadmap, which interestingly mentioned the K12 chip. The K12 was actually an ARMv8 64-bit SoC, whose design was led by Jim Keller back in 2016. Though not explicitly stated, it is very much possible that this particular patent refers to x86_64 CPU clusters. It could be that AMD could have taken some cues from the K12's big.LITTLE design.

Source(s)

Free Patents Online (PDF) via @Underfox3 on Twitter