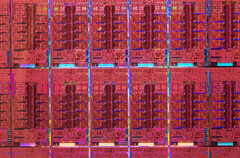

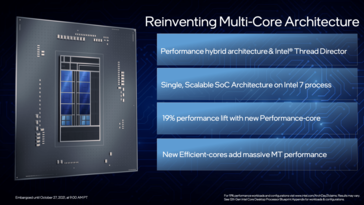

After numerous rounds of leaks, it's finally here. Intel has taken wraps off the new 12th generation Alder Lake-S processor lineup for desktops. During the presentation, Intel's Marcus Kennedy offered an overview of what makes Alder Lake tick and how the heterogeneous architecture comprised of Golden Cove Performance (P)-cores and Gracemont Efficiency (E)-cores work in the system.

Heterogeneous ISA, now on mainstream desktop

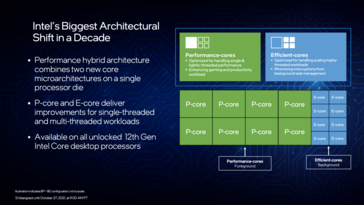

Intel says the P-cores are optimized for single and lightly-threaded apps such as games and general productivity foreground tasks while the E-cores are geared towards workloads with many threads. The E-cores also can help with managing background tasks while the P-cores focus more on the performance aspects. This isn't too unlike the big.LITTLE approach that ARM processors have had for years.

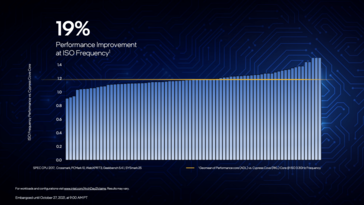

Intel said that this architecture shift can offer up to a 19% improvement over the previous generation Cypress Cove cores in Rocket Lake at the same frequency.

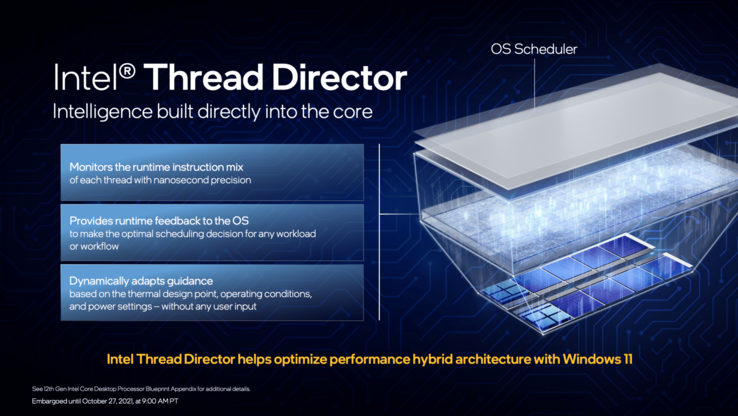

Intel Thread Director

While mobile operating systems are built from the ground up to be aware of heterogeneous architectures, the situation is different on a desktop. Therefore, Intel has built its own way of directing threads to the relevant core.

Called Intel Thread Director, this allows the OS scheduler to be aware of the presence of different ISAs on the same SoC and effectively manage resources. Intel said that Thread Director takes several parameters into account such as TDP, available power, etc. and provides continuous feedback to the OS scheduler with "nanosecond precision".

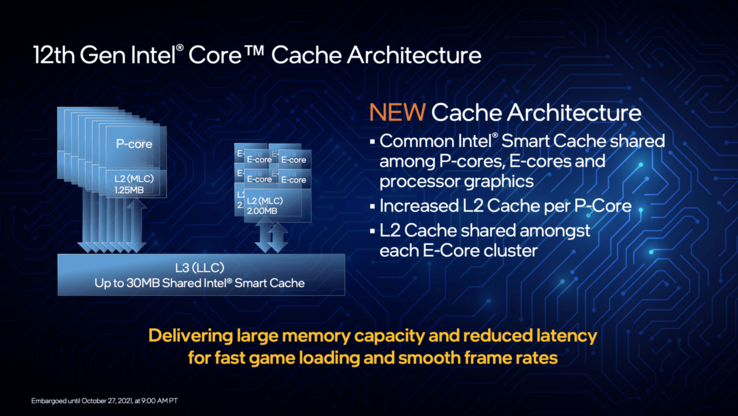

Common 30 MB L3 cache for P-cores and E-cores

Given the use of two ISAs, Intel has also reworked its cache topology for the 12th gen. The 11th gen Rocket Lake used Cypress Cove cores, which were essentially 10 nm Sunny Coves backported to 14 nm. Cypress Cove offered eight cores each with a 512 KB L2 cache and a 2 MB L3 cache. With Alder Lake, each P-core gets a 1.25 MB L2 cache while each E-core cluster gets a shared 2 MB L2 cache. We think this means a set of four E-cores would share a single L2 cache, but we will confirm this soon with Intel.

Apart from dedicated L2 caches, Alder Lake also sports a 30 MB shared L3 cache across both core types and the integrated GPU for reduced latency. Though not exactly an apples-to-apples comparison, we have seen how the shared L3 cache offers immediate performance benefits in the case of AMD Ryzen 5000 Zen 3 processors.

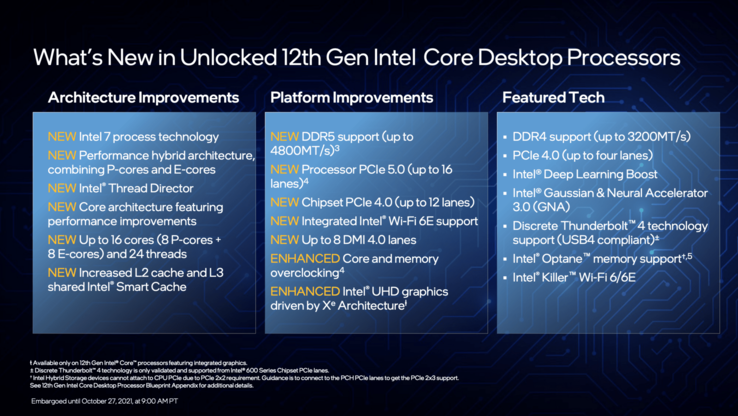

12th gen platform features — No PCIe Gen5 on the chipset

Alder Lake is based on a 10 nm Enhanced SuperFin process, now known as Intel 7. On the desktop, the flagship Core i9-12900K will offer up to 16 cores and 24 threads — 8 P-cores that support hyperthreading and 8 E-cores that don't.

The CPU supports DDR5-4800 RAM, and we've also been seeing various DDR5 kit announcements from OEMs. That being said, DDR4-3200 memory works just fine too.

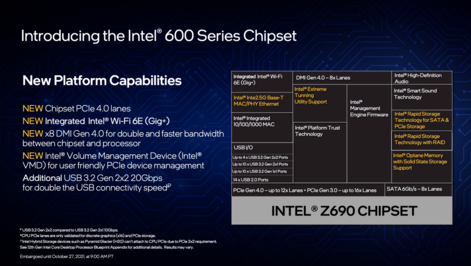

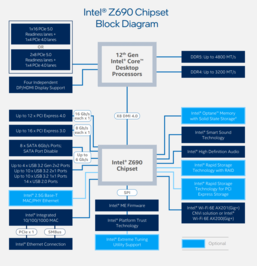

The Alder Lake processors also offers up to 16 lanes of PCIe Gen5 connectivity. However, the 600 series chipsets can support only up to 12 lanes of PCIe Gen4. The exact reasons for cutting down on PCIe Gen5 for the 600 series chipsets, including the flagship Z690 chipset, is not fully clear. It could be that Intel thought such as implementation would drive up prices, not to mention power consumption

Besides, even a GPU such as the NVIDIA GeForce RTX 3090 can hardly saturate PCIe Gen3 x16. That being said, storage is a good benefactor of increased I/O, so we might see some new NVMe drives that can possibly utilize a good amount of the bandwidth, which in case you're wondering is about 128 GB/s aggregate over 16 lanes.

In total, the Z690 chipset can offer up to 28 PCIe lanes — 16 Gen3 and 12 Gen4. Apart from these, there are eight lanes for Direct Media Interface (DMI) 4.0. For those not in the know, DMI is a fancy term for the link between the processor and the platform controller hub (PCH) aka the chipset (Northbridge and Southbridge, anyone?).

There is also support for up to 4x USB 3.2 Gen2x2, 10x USB 3.2 Gen2, 10x USB 3.2 Gen1, and 14 USB 2.0 ports, so connectivity shouldn't be an issue at all. Finally, there are eight lanes of SATA 6 Gb/s ports for storage expansion.

Source(s)

Intel Press Brief

Deutsch

Deutsch English

English Español

Español Français

Français Italiano

Italiano Nederlands

Nederlands Polski

Polski Português

Português Русский

Русский Türkçe

Türkçe Svenska

Svenska Chinese

Chinese Magyar

Magyar