At Intel's Architecture Day earlier this week, key Intel executives Raja Koduri, Jim Keller, Murthy Renduchintala, and others provided a glimpse into new Intel technologies that will pave the roadmap for upcoming client and server CPUs and other silicon. While Intel spoke about a host of new developments slated to arrive in process, architecture, memory, interconnects, security, and software, most of them center around Intel's new 3D package technology called 'Foveros'. Intel also spoke at length about its new 10nm 'Sunny Cove' microarchitecture that will feature in Xeon and Core CPUs in the later half of 2019. Let's look at them in more detail below.

Increasing package density with 'Foveros'

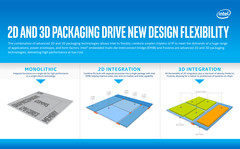

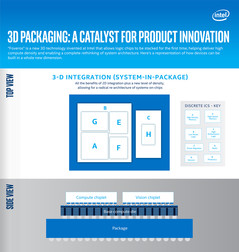

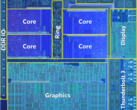

Most CPUs today are monolithic dies that have all components on a single package in a planar dimension. We've recently seen 2D packaging systems where multiple chips are embedded on a package connected via a high-speed interconnect such as EMIB as was in the case of the Intel Core i7-8809G. Now, Intel is talking 3D packaging wherein heterogeneous chips can be stacked on top of each other connected via a new active interposer. So essentially, you can have much more powerful CPU, GPU, and AI processors or even mix and match technology IP as desired. The components can be broken down into 'chiplets' in which I/O, SRAM, and power deliver circuits (essentially a full PCH) become part of the active interposer on top of which the logic processors are stacked.

Intel says it is ready for mass scale manufacturing of Foveros chips for availability by 2H 2019. The first such product will combine a 10nm stacked chiplet with a 22FFL base die.

From Lakes to Coves — Going 10nm with 'Sunny Cove'

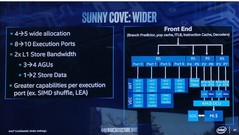

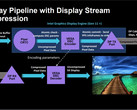

After a series of delays, Intel is finally ready to transcend the 14nm barrier with its new 10nm process. The new CPU family is being called 'Sunny Cove' and will comprise both Intel Xeon server and Intel Core client CPUs. Sunny Cove will feature both general purpose performance improvements such increase in IPC and/or frequency, along with special purpose performance boosts such as optimization of specific workloads using specialized instructions.

Sunny Cove will see increased IPC for single-thread code, which has been more or less the same since Skylake till the recent Whiskey Lake. This means, a perceivable improvement should be seen in almost every workload as long as it is compute-bound. On the back end, Sunny Cove will offer improvements for more parallel operations and reduced latency. The L1 cache is now 50 percent larger than Skylake along with the cache for decoded micro-ops and L2. Exact sizes will depend on the SKU.

Sunny Cove also increases the number of reservation stations from two in Skylake to four and consequently, the number of ports for dispatching instructions have been increased from eight to ten. Each cycle in Skylake dispatched a maximum of four instructions while Sunny Cove can now dispatch five. The new architecture will also sport two additional execution units capable of handling LEA instructions and vector shuffles. Support for the AVX-512 instruction set is built-in.

Sunny Cove can now address 4 PB (yes, Petabytes) of physical memory from the current 256 TB limit and up to 128 PB of virtual address space on the 64-bit architecture.

Intel says that the first Sunny Cove-based Core CPUs will debut in 2H 2019. This will be succeeded by Willow Cove in 2020, which is expected to offer a redesigned cache, extra security, and a new transistor optimization. In 2021, we will see Golden Cove with improved single-threaded performance and an improved focus on ML, security, networking, and 5G. Xeon will also see a Sunny Cove implementation in the form of Ice Lake but details are still scarce at this point.

Deutsch

Deutsch English

English Español

Español Français

Français Italiano

Italiano Nederlands

Nederlands Polski

Polski Português

Português Русский

Русский Türkçe

Türkçe Svenska

Svenska Chinese

Chinese Magyar

Magyar